## Scaling junctionless multigate field-effect transistors by step-doping

Yi Song and Xiuling Li

Citation: Applied Physics Letters 105, 223506 (2014); doi: 10.1063/1.4902864

View online: http://dx.doi.org/10.1063/1.4902864

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/105/22?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Graphene nanopore field effect transistors

J. Appl. Phys. **116**, 023709 (2014); 10.1063/1.4889755

Planar junctionless transistor with non-uniform channel doping

Appl. Phys. Lett. 102, 133505 (2013); 10.1063/1.4801443

Self-aligned graphene field-effect transistors with polyethyleneimine doped source/drain access regions

Appl. Phys. Lett. 101, 183113 (2012); 10.1063/1.4765658

Junctionless multigate field-effect transistor

Appl. Phys. Lett. 94, 053511 (2009); 10.1063/1.3079411

Instability of the Noise Level in Polymer FieldEffect Transistors with NonStationary Electrical Characteristics

AIP Conf. Proc. 665, 488 (2003); 10.1063/1.1584925

## Scaling junctionless multigate field-effect transistors by step-doping

Yi Song and Xiuling Lia)

Department of Electrical and Computer Engineering and Micro and Nanotechnology Laboratory, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, USA

(Received 7 October 2014; accepted 15 November 2014; published online 2 December 2014)

Conventional junctionless (JL) multigate field-effect transistors (MuGFETs) use extremely scaled and highly doped fins as channels. Such small fins introduce large parasitic resistance as well as performance fluctuation due to fin width variations. The high channel doping significantly reduces bulk carrier mobility, which reduces on-state current and escalates short channel effect related leakage. In this letter, we present a step-doping scheme for the scaling of JL MuGFETs. By employing a two-step-doping profile, with the high doping side near the gate, higher threshold voltage and better off-state performance can be achieved, along with higher on-state current. This opens a route for threshold voltage design and addresses the design optimization for both on-state current and off-state leakage for JL MuGFETs. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4902864]

Junctionless (JL) multigate field-effect transistors (MuGFETs) have been proposed as a potentially better alternative to traditional inversion mode MOSFETs for its scalability and fabrication simplicity.<sup>2,3</sup> Conventional JL MuGFET design involves a uniformly doped channel at a high level (typically  $N_D > 10^{19} cm^{-3}$ ) in order to deliver high current per unit width and minimize source/drain resistance (R<sub>SD</sub>). However, the on-current improvement by increasing N<sub>D</sub> reaches a limit because bulk conduction carrier mobility is degraded due to the increased impurity scattering. The device is getting more and more difficult to turn off as N<sub>D</sub> increases, because higher gate bias is required to deplete the entire channel. The ultrahigh channel doping concentration will also enhance coupling between drain and channel, which can induce significant drain induced barrier lowering effects (DIBL).

Shrinking the dimension of the fins would help to alleviate the problems; however, the design rules will be tightened. Both the width and thickness of the fins have to be extremely scaled due to the reduced maximum depletion width, W<sub>DW</sub>, as  $N_D$  increases.<sup>5</sup> For example, the fin width needs be as small as 5 nm when  $N_D = 8 \times 10^{19} \, \text{cm}^{-3}$  for better gate electrostatic control.<sup>6-8</sup> Such a small fin is difficult to fabricate<sup>9</sup> and would deteriorate the conduction current by introducing large parasitic resistance. It may also lead to the swing of threshold voltage due to the potentially larger process variation for smaller scales. 10 The potential threshold swing issue is even worse for JL FETs compared with inversion-mode devices, since JL devices are more sensitive to fin width variability. 11 Introducing non-uniform dopant distribution profiles in the channel is promising, as reported in planar JT devices using a Gaussian doping profile, 12 which showed improvement of the off-current at some expense of the oncurrent. More systematic design and analysis are needed, especially for JT MuGFETs.

In this letter, we present a design that adopts stepdoping scheme in JL MuGFETs, with higher doping concentration on both the top surface as well as the side walls of

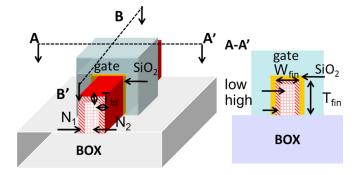

A JL MuGFET structure employing step-doping profile is schematically shown in Fig. 1. The cross sectional view along A-A' direction shows the two regions with different doping concentrations, high (N1, near-surface or shell, shaded with hash lines) and low (N<sub>2</sub>, subsurface or core, shaded with grids) as indicated. We will call this the step-doping if it is high to low doped from the surface down; on the contrary, retrogradedoping<sup>13</sup> refers to low to high. For ease of analysis, we assume that the high and low doped regions have the same area A, i.e.,  $(T_{fin} - T_{td}) \times (W_{fin} - T_{td}) = T_{fin} \times W_{fin}/2$ , where  $T_{fin}$  and W<sub>fin</sub> are the total thickness and width of the fin, respectively, and T<sub>td</sub> is the transition depth. For comparison, we use a control design with the same total number of dopants, but uniformly doped with doping concentration of  $(N_1 + N_2)/2$ . 3D numerical simulation of the device DC performance was carried out using Synopsis Sentaurus at 300 K. The parameters

FIG. 1. Schematic of a step doped JL MuGFET structure, The cross sectional view (along A-A') indicates two different doping regions inside the channel.  $T_{\rm fin}$  and  $W_{\rm fin}$  are the total thickness and width of the fin, respectively, and  $T_{\rm td}$  is the transition depth.

fins. Comparison with uniform-doping and retrograde-doping reveals that the high-low step-doping is superior in terms of better threshold voltage control, lower off-state leakage, higher on-current with the same total number of dopants, and better short channel effects (SCEs) immunity. We then discuss the underlying mechanism of such improvements and define a scaling factor metric to quantify its improved scalability. The implementation of step-doping could be useful for the scaling of JL MuGFETs.

a)Electronic mail: xiuling@illinois.edu

TABLE I. Summary of structure design parameters for the simulation of JL MuGFETs.

|                                          | Uniform               | Retrograde-doping                     | Step-doping                           |

|------------------------------------------|-----------------------|---------------------------------------|---------------------------------------|

| Channel doping (cm <sup>-3</sup> )       | $2.75 \times 10^{19}$ | $5 \times 10^{18} / 5 \times 10^{19}$ | $5 \times 10^{19} / 5 \times 10^{18}$ |

| Gate oxide (nm)                          | 2                     | 2                                     | 2                                     |

| Gate workfunction (eV)                   | 5.5                   | 5.5                                   | 5.5                                   |

| Transition depth (T <sub>td</sub> ) (nm) | N/A                   | 2                                     | 2                                     |

| $T_{fin}$ (nm)                           | 20                    | 20                                    | 20                                    |

| $W_{fin}$ (nm)                           | 9                     | 9                                     | 9                                     |

| L <sub>gate</sub> (nm)                   | 10-170                | 10-170                                | 10-170                                |

| W <sub>DM</sub> (nm)                     | 7.2                   | 5.5                                   | 15                                    |

used for simulation of a Si channel are summarized in Table I. Band-to-band tunneling <sup>14</sup> and mobility degradation due to impurity scattering were taken into account. <sup>15</sup> Quantum mechanical correction was not included to save simulation time and should not affect the analysis on different doping schemes. Note that the proposed structure can be readily fabricated either by advanced implantation and annealing technology or by *in situ* doping during epitaxial growth.

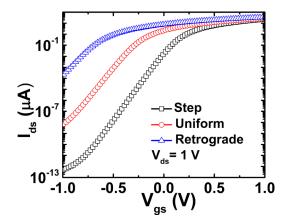

Shown in Fig. 2 are the simulated transfer curves  $I_{ds}$ - $V_{gs}$  for aforementioned devices ( $L_g=15\,\text{nm}$ ) but with three different doping schemes. At  $V_{ds}=V_{DD}=1\,V$  and  $V_{gs}=V_{th}+2/3V_{DD}$ ,  $I_{on}$  is found to be 650, 480, and 370  $\mu\text{A}/\mu\text{m}$  for step doping, uniform doping, and retrograde doping, respectively, normalized by the fin height. This can be understood because  $I_{on}$  can be estimated from the following equation:

$$I_{on} \approx \sum q \mu N \frac{T_{fin} W_{fin}}{L_g} V_{DD},$$

(1)

where  $\mu$  is the mobility, N is the carrier concentration,  $L_g$  is the gate length,  $V_{DD}$  is the supply voltage, and  $\Sigma$  accounts for the summation of the conducting carriers with different  $\mu$ . Although the total amount of conducting charges in the channels is the same for three designs, the different dopant distribution changes the effective fin width. For the step-doping case, the gate bias converts the channel from depletion to flat band, then to accumulation mode faster because of a smaller effective fin width which will be discussed further later. This leads to more carriers for the same amount of gate voltage overdrive. On the other hand, the mobility difference between the highly doped areas  $(2.75 \times 10^{19})$  and

FIG. 2. Comparison of the transfer  $I_{ds}$ - $V_{gs}$  curves for different doping schemes with  $L_e=15\,\text{nm}$  and the detailed parameters adopted from Table I.

$5 \times 10^{19} \, \mathrm{cm}^{-3}$ ) is not significant, <sup>16</sup> while the mobility in the lower doped area ( $5 \times 10^{18} \, \mathrm{cm}^{-3}$ ) is much higher which contributes to more current. Therefore, a higher on-current in the step doping scheme is expected.

Furthermore, the sub-threshold behaviors show significant improvement. The subthreshold slope (SS) is lowered to 88 mV/dec for the step-doping scheme from 98 mV/dec for the uniform doping scheme, with the retrograde-doping scheme being the worst at 107 mV/dec. Correspondingly, the step-doping scheme has the lowest off-state current compared with the other two.

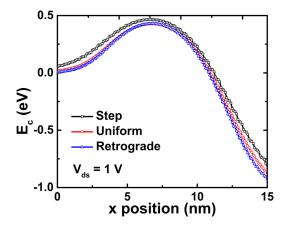

The source barrier, which is the maximum difference of the off-state conduction band minimum  $E_c$  in the source/channel region, determines the off-state current. Fig. 3 plots the off-state  $E_c(x)$  at the interface of Si and  $SiO_2$  along the middle of the fin channel (i.e., along B-B' in Fig. 1). Both the height and the width of source barrier are slightly larger for the step-doping scheme compared with the other two. Although the difference is small, it may still block the tunneling at off-state more effectively, contribute to lower leakage current.

In addition, the threshold voltage ( $V_{th}$ ) becomes more and more negative, from step, uniform, to retrograde-doping structures, as can be seen from Fig. 2. This could be attributed to the slope of electric field (dE/dx) in the channel. The lower doped region is located away from the gate metal in the step-doping case, resulting in a reduced dE/dx thus smaller surface potential  $\phi_s^{17}$  compared with the other two. Therefore, lower  $V_{th}$  value can be achieved according to Gauss' law (note that the total charge is identical for all cases). This feature is useful for the scalability of JL transistors because it can help turn off transistors without the need of excessively high gate workfunction or scaled fin dimensions.

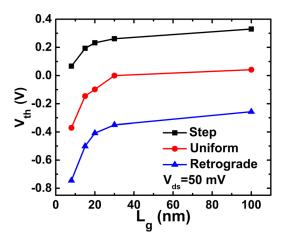

Fig. 4 examines the SCEs by plotting the  $V_{th}$  roll-off as a function of gate lengths  $(L_g)$ . The steep decay of  $V_{th}$  for small  $L_g$  can be seen for all doping schemes, but the decay rate is the slowest for the step-doping structure. The trends of SS and DIBL as a function of  $L_g$  are also examined and shown in Fig. 5. The step-doping structure shows the lowest SS and DIBL across the entire  $L_g$  range. Clearly, the step-doping scheme leads to better SCE immunity.

FIG. 3. Comparison of conduction band minimum  $E_c$  versus positions in the channel (along B-B' in Fig. 1) at off-state ( $V_{\rm gs} = V_{\rm th} - 1/3*V_{\rm DD}$ ), for different doping schemes with  $L_{\rm g} = 15$  nm that source at zero and drain at 15 nm in x-axis. The detailed device parameters are adopted from Table I.

FIG. 4. Comparison of threshold voltage (V<sub>th</sub>) roll-off with the scaling of the gate length (Lg) between the three different doping schemes.

We believe that the improved SCE immunity results from the smaller effective fin width "seen" by the gate electrode in step-doping and better gate electrostatic control. On one hand, the thicker W<sub>fin</sub> is, the larger current it can deliver per fin. The maximum W<sub>fin</sub> is, however, limited by the maximum depletion width W<sub>DM</sub> in order to ensure total depletion at off-state. On the other hand, lower channel doping concentration, i.e., larger W<sub>DM</sub>, is desired in order to improve SS, DIBL, and lower leakage for the same W<sub>fin</sub>. <sup>4</sup> To evaluate the extent of depletion in the channel, we define an effective fin width scale factor  $\alpha = W_{fin}/W_{DM}$ . The smaller  $\alpha$ , the easier the channel can be turned off by complete depletion, which means stronger gate electrostatic control and better SCE immunity.

We compare  $\alpha$  for the three doping schemes (1)  $N_1 > N_2$ ; (2)  $N_1 = N_2$ ; and (3)  $N_1 < N_2$ , where  $N_1$  and  $N_2$  are the near-surface and subsurface doping concentrations, respectively, as indicated in Fig. 1. We assume that (1) and (3) have the same transition depth  $T_{td}$  for comparison and  $T_{td} < W_{DM,N1}$ . By integrating Poison's equation along the normal direction of oxide/Si interface,<sup>5</sup> we can calculate the effective W<sub>DM</sub> for an arbitrary two-step-doping scheme

$$W_{DM,non-uniform} = \sqrt{T_{td}^2 - \frac{N_1}{N_2} T_{td}^2 + \frac{2\varepsilon_{si}}{qN_2}} \varphi_s, \qquad (2)$$

$$\begin{array}{c} 320 \\ - \\ 80 \\ - \\ 160 \\ - \\ 80 \\ - \\ 120 \\ - \\ 160 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200 \\ - \\ 200$$

FIG. 5. Subthreshold slop (Ss) and Drain Induced Barrier Lowering (DIBL) comparison verse gate length using the same parameters in Table I.

where  $\varphi_s=rac{kT}{q}(\lnrac{N_1}{n_i}+\lnrac{N_2}{n_i}).$  We substituted  $N=(N_1+N_2)/2$  in (2) to obtain the value of W<sub>DM</sub>,2 for the uniform-doping scheme. We found that  $W_{DM,1} > W_{DM,2} > W_{DM,3}$  holds true only when  $N_1 > N_2$ . The calculated values of  $W_{DM}$  are 15, 7.2, and 5.5 nm for step, uniform, and retrograde-doping schemes, respectively, using parameters listed in Table I. Since the physical thicknesses W<sub>fin</sub> are all identical for these three schemes, we can deduce that  $\alpha 1 < \alpha 2 < \alpha 3$ . Therefore, the step-doping scheme yields the smallest  $\alpha$  thus the best off-state control. This also implies that if the same off-state performance is designed for all three schemes, wider fins for the step-doping scheme can be allowed. As a result, step-doping scheme leads to better scalability, by relaxing device fabrication requirements which also should reduce parasitic resistance.

In this letter, we presented a step-doping scheme for the scaling of JL transistors. Lower |V<sub>th</sub>|, higher I<sub>on</sub>/I<sub>off</sub> ratio, and better SCE immunity can be achieved with the high-low step-doping in the channel. The standby power consumption is significantly reduced while achieving higher on-state current. The benefits brought by stepdoping are attributed to the reduction of effective fin width. This design methodology relaxes the requirement for fin width scaling in JL MuGFETs, allowing continued scaling of JL transistors.

This work was supported by the Office of Naval Research Young Investigator Program Award No. N000141110634 and the NSF ECCS Award No. #1001928.

<sup>1</sup>B. Sorée, W. Magnus, and G. Pourtois, J. Comput. Electron. 7(3), 380 (2008)

<sup>2</sup>J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, and R. Murphy, Nat. Nanotechnol. 5(3), 225 (2010).

<sup>3</sup>Y. Song, C. Zhang, R. Dowdy, K. Chabak, P. K. Mohseni, W. Choi, and X. Li, IEEE Electron Device Lett. 35(3), 324 (2014).

<sup>4</sup>R. Trevisoli, R. T. Doria, M. de Souza, and M. A. Pavanello, Appl. Phys. Lett. 103(20), 202103 (2013).

<sup>5</sup>S. M. Sze and K. K. Ng, Physics of Semiconductor Devices, 3rd ed. (Wiley-Interscience, 2007).

<sup>6</sup>L. Ansari, B. Feldman, G. Fagas, J.-P. Colinge, and J. C. Greer, Appl. Phys. Lett. 97(6), 062105 (2010).

<sup>7</sup>L. Ansari, B. Feldman, G. Fagas, J.-P. Colinge, and J. C. Greer, Solid-State Electron. 71, 58 (2012).

<sup>8</sup>C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J.-P. Colinge, Appl. Phys. Lett. 94, 053511 (2009).

S. Barraud, M. Berthome, R. Coquand, M. Casse, T. Ernst, M.-P. Samson, P. Perreau, K. K. Bourdelle, O. Faynot, and T. Poiroux, IEEE Electron Device Lett. 33(9), 1225 (2012).

<sup>10</sup>J.-P. Colinge, A. Kranti, R. Yan, C.-W. Lee, I. Ferain, R. Yu, N. D. Akhavan, and P. Razavi, Solid-State Electron. 65-66, 33-37 (2011).

<sup>11</sup>G. Leung and C. On Chui, IEEE Electron Device Lett. 32(11), 1489

<sup>12</sup>P. Mondal, B. Ghosh, and P. Bal, Appl. Phys. Lett. 102(13), 133505 (2013).

<sup>13</sup>B. Ho, X. Sun, C. Shin, and T.-J. Liu, IEEE Trans. Electron Devices 60(1), 28 (2013).

<sup>14</sup>S. Gundapaneni, M. Bajaj, R. K. Pandey, K. V. R. M. Murali, S. Ganguly, and A. Kottantharayil, IEEE Trans. Electron Devices 59(4), 1023 (2012).

<sup>15</sup>SENTAURUS TCAD version D-2010.03, Synopsis, Inc., Mountain View,

<sup>16</sup>C. Jacoboni, C. Canali, G. Ottaviani, and A. A. Quaranta, Solid-State Electron. 20(2), 77 (1977).

<sup>17</sup>R. D. Trevisoli, R. T. Doria, M. de Souza, and M. A. Pavanello, Semicond. Sci. Technol. 26(10), 105009 (2011).